Предварительно

# Микросхема интегральная 1508ПЛ8Т. Техническое описание.

# **АННОТАЦИЯ**

Микросхема интегральная 1508ПЛ8Т представляет собой двухканальный цифровой вычислительный синтезатор (ЦВС, DDS, Direct Digital Synthesizer). Обеспечивает формирование гармонических квадратурных колебаний и сигналов с линейно-частотной модуляцией (ЛЧМ), амплитудно-фазовой (QAM), частотной и фазовой манипуляцией (ЧМ и ФМ) на частоте дискретизации до 1 ГГц.

# СОДЕРЖАНИЕ

| 1. | Основные особенности                            |    |

|----|-------------------------------------------------|----|

|    | 1.1. Состав микросхемы                          |    |

|    | 1.2. Основные технические характеристики:       |    |

|    | Условное графическое обозначение                |    |

| 3. | Функциональное описание                         |    |

|    | 3.1. Режим синтеза гармонического сигнала       | 8  |

|    | 3.2. Режим модуляции                            | 9  |

|    | 3.3. Режим синтеза ЛЧМ сигнала                  | 9  |

|    | 3.3.1. Режим коррекции                          |    |

| 4. | Выводы БИС                                      |    |

|    | 4.1. Назначение выводов                         |    |

|    | 4.2. Расположение выводов.                      |    |

|    | 4.3. Назначение выводов SEL в различных режимах |    |

| 5  | Внутреннее адресное пространство.               |    |

| ٥. | 5.1. Адресное пространство управления DDS       | 13 |

|    | 5.2. SWRST                                      | 15 |

|    | 5.3. DEVID                                      |    |

|    | 5.4. SEL REG                                    |    |

|    |                                                 |    |

|    | 5.5. CTR                                        |    |

|    | 5.6. SYNC                                       |    |

|    | 5.7. CLR                                        |    |

|    | 5.8. LINK                                       |    |

|    | 5.9. ROUTE                                      |    |

|    | 5.10. CHx_TSW                                   |    |

|    | 5.11. CHx_dPhy_L                                |    |

|    | 5.12. CHx_dPhy_M                                |    |

|    | 5.13. CHx_dPhy_H                                |    |

|    | 5.14. CHx_Py                                    |    |

|    | 5.15. CHx_Muly                                  | 18 |

|    | 5.16. CHx_Offsety                               | 18 |

|    | 5.17. CHx_dPh_all_L                             | 18 |

|    | 5.18. CHx_dPh_all_M                             | 18 |

|    | 5.19. CHx_dPh_all_H                             | 18 |

|    | 5.20. CHx_P_all                                 | 18 |

|    | 5.21. CHx_Mul_all                               |    |

|    | 5.22. CHx Offset all                            |    |

|    | 5.23. CHx_LS_CTR                                |    |

|    | 5.24. CHx_LS_CRFMIN                             |    |

|    | 5.25. CHx_LS_F1(2)_L(M, H)                      | 19 |

|    | 5.26. CHx LS Ph1(2)                             |    |

|    | 5.27. CHx_LS_dFy_L                              |    |

|    | 5.28. CHx_LS_dFy_M                              |    |

|    |                                                 |    |

|    | 5.29. CHx_LS_dFy_H                              |    |

|    |                                                 |    |

|    | 5.31. CHx_LS_TPH2_L(M, H)                       |    |

|    | 5.32. CHx_LS_TPH3_L(M, H)                       |    |

| _  | 5.33. CHx_LS_TPH4_L(M, H)                       |    |

| 6. | Описание интерфейсов                            |    |

|    | 6.1. Параллельный порт управления DDS.          |    |

|    | 6.2. Линк-порт                                  |    |

|    | 6.2.1. Формат данных:                           |    |

|    | 6.2.2. Управление скоростью                     |    |

|    | 6.3. Последовательный порт управления DDS       | 23 |

|    | 6.4. Цифро-аналоговый преобразователь           | 24 |

| 7. | Типовые схемы включения                         | 25 |

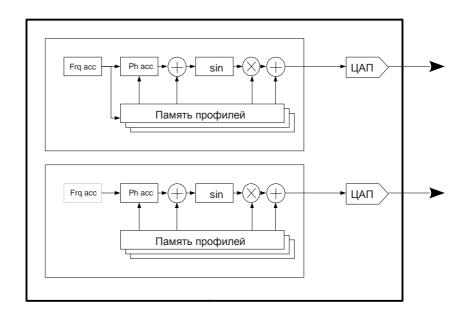

|    | 7.1. Двухканальный режим                        | 25 |

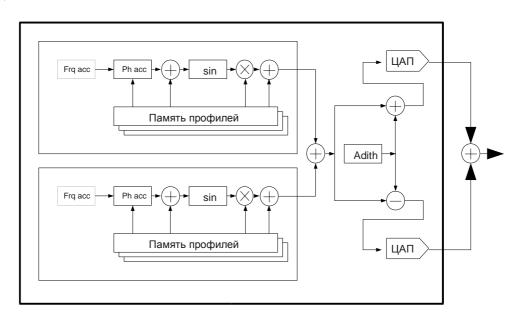

|    | 7.2. Одноканальный режим                        |    |

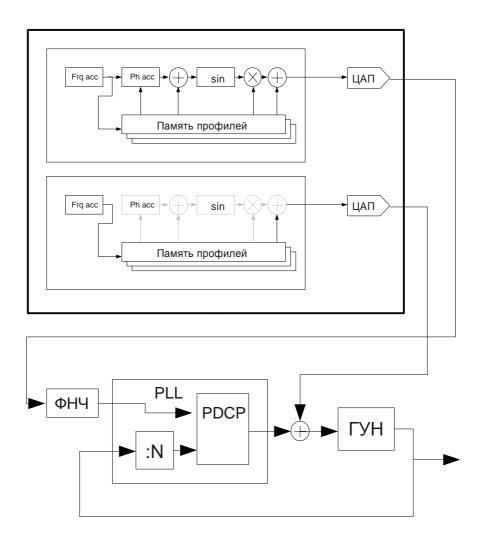

|    | 7.3. Режим ЛЧМ с умножением частоты             |    |

# ОАО НПЦ "ЭЛВИС"

| 8. | Электрические характеристики | 28 |

|----|------------------------------|----|

| 9. | Временные характеристики     | 30 |

#### 1. ОСНОВНЫЕ ОСОБЕННОСТИ

#### 1.1. Состав микросхемы

- Два независимых канала синтеза;

- **ñ** Программируемый делитель тактовой частоты;

- **ñ** Приемник тактового сигнала с пониженным джиттером;

- **n** Быстродействующий компаратор;

- **п** Последовательный синхронный порт;

- ñ 16-битный параллельный порт;

- **ñ** 4-разрядный линк-порт;

- **n** Интерфейс прямого управления;

- **ñ** Устройство синхронизации

#### 1.2. Основные технические характеристики:

- Частота дискретизации двух независимых каналов 1 ГГц;

- 64 профиля модуляции сигнала в каждом канале;

- ñ 2 профиля ЛЧМ

- **ñ** Независимое управление частотой, фазой, амплитудой, постоянным смещением каждого канала;

- **ñ** Два 10-битных ЦАП;

- **ñ** Аккумулятор частоты 48 бит.

- $\tilde{\mathbf{n}}$  Аккумулятор фазы 48 бит

- **n** 16-разрядный регистр управления смещением фазы;

- **ñ** 13-разрядный четырехквадрантный амплитудный модулятор;

- **ñ** 12-разрядный регистр управления постоянным смещением выходного сигнала;

- **ñ** Кусочно-линейная коррекция параметров сигнала в режиме ЛЧМ;

- **ñ** Возможность рандомизации фазы и амплитуды;

- **ñ** Возможность синхронизации нескольких микросхем;

- **ñ** Возможность «плавного» переключения параметров модуляции

- 1.8 В напряжение питания ядра;

- **ñ** 3.3 В напряжение буферов входов и выходов;

- ñ 1.8, 3.3 В напряжение питания ЦАП;

- **ñ** 3.3 В напряжение питания компаратора;

# 2. УСЛОВНОЕ ГРАФИЧЕСКОЕ ОБОЗНАЧЕНИЕ

|   | IREF1      |     | CMP_OP |  |

|---|------------|-----|--------|--|

|   | IREF2      |     | CMP_OM |  |

|   | RSTn       | DDS |        |  |

|   | CLKP       |     |        |  |

|   | CLKM       |     |        |  |

| _ | CLKDP      |     |        |  |

|   | CLKDM      |     |        |  |

|   | CMP_INP    |     |        |  |

|   | CMP_INM    |     |        |  |

| _ | SEL1[5:0]  |     |        |  |

|   | SEL2[5:0]  |     |        |  |

|   | SDI        |     | OUTP1  |  |

| _ | SDO        |     | OUTM1  |  |

| _ | SCK        |     |        |  |

|   | SCSn       |     | OUTP2  |  |

| _ | WRn        |     | OUTM2  |  |

|   | RDn        |     |        |  |

| _ | CSn        |     |        |  |

|   | ADR        |     |        |  |

| _ | DATA[15:0] |     |        |  |

|   | CMP_VDD    |     |        |  |

|   | CMP_GND    |     |        |  |

|   | CVDD       |     |        |  |

|   | CGND       |     |        |  |

|   | PVDD       |     |        |  |

|   | PGND       |     |        |  |

|   | AVDD       |     |        |  |

|   | DVDD       |     |        |  |

| _ | AVDD       |     |        |  |

| _ | AVDD1      |     |        |  |

| _ | AVDD2      |     |        |  |

| _ | DVDD1      |     |        |  |

|   | DVDD2      |     |        |  |

|   | AGND       |     |        |  |

Сумматор 2

Коммутатор

Гауссов

Схема

линейной

Выходной коммутатор

Параллельный

порт

Последовательный

Компаратор

WRn

CMP INF

# 3. ФУНКЦИОНАЛЬНОЕ ОПИСАНИЕ CLKOP C

Преобразователь

ф аза-амплитуда

Память профилей ЛЧМ (2 профиля)

Память профилей

модуляции (64 профиля)

Схема

**управления**

канала

Рис. 3.1: Функциональная диаграмма 1508ПЛ8Т

Канап 2

**Умножитель**

Цифровой синтезатор содержит два идентичных канала («Канал 1» и «Канал 2»), реализующих функции формирования модулированного сигнала в цифровой области, два цифро-аналоговых преобразователя (ЦАП1, ЦАП2), выходной коммутатор, параллельный 16-разрядный порт, последовательный синхронный порт, линк-порт, схемы управления и синхронизации. Также на кристалле находится компаратор.

Параллельный и последовательный порты позволяют осуществлять запись и чтение конфигурационных регистров синтезатора для задания режимов, тестирования и осуществления модуляции сигнала.

Линк-порт позволяет осуществлять модуляцию сигнала и задавать скорость следования модулирующих символов.

Каждый канал содержит 48-разрядный аккумулятор частоты, 48-разрядный аккумулятор фазы, память профилей профилей ЛЧМ (2 профиля), память профилей модуляции (64 профиля), схему линейной интерполяции, гауссов фильтр, генератор фазового выбеляющего шума, схемы управления.

Аккумулятор частоты имеет разрядность 48 бит, выходная разрядность 48 бит.

Аккумулятор фазы имеет разрядность 48 бит, выходная разрядность 17 бит.

Сумматор 1 имеет входную разрядность 17 бит (текущая фаза), 16 бит (смещение фазы), 4 бита (выбеляющий шум). Выходная разрядность – 15 бит.

Преобразователь фаза — амплитуда имеет входную разрядность  $15 \, \text{бит}$ , выходную разрядность —  $12 \, \text{бит}$ .

Умножитель имеет входную разрядность 12 бит (текущая амплитуда), 13 бит (коэффициент усиления), выходная разрядность 12 бит.

Сумматор 2 имеет входную разрядность 12 бит, выходную разрядность – 12 бит.

Каждый из 64 профилей модуляции содержит 48-разрядный регистр приращения фазы (dPh), 16-разрядный регистр смещения фазы (P), 13-разрядный регистр амплитуды (Mul) и 12-разрядный регистр постоянного смещения (Offset) синтезируемого сигнала. В режиме синтеза ЛЧМ память профилей может использоваться для хранения узловых значений параметров частотно-зависимой коррекции.

Профиль ЛЧМ содержит 48-разрядный регистр приращения частоты, 48-разрядный регистр начальной частоты и 16-разрядный регистр начальной фазы.

Гауссов фильтр осуществляет фильтрацию параметров модуляции. Длина импульсной характеристики данного фильтра задается регистром TSW.

Схема линейной интерполяции используется в режиме коррекции при синтезе ЛЧМ и осуществляет вычисление значений параметров коррекции для промежуточных частот методом кусочно-линейной интерполяции. Такая коррекция позволяет скомпенсировать искажения АЧХ ЦАП вида  $\sin(x)/x$ , а также ввести произвольные предыскажения для компенсации погрешностей аналоговой части тракта.

Выходной коммутатор осуществляет, в зависимости от режима, суммирование сигналов с выходов каналов, добавление амплитудного шума и ограничение разрядности сигнала с 12 бит до 10 бит перед подачей на соответствующий ЦАП.

Компаратор может использоваться для преобразования гармонического синтезированного сигнала в прямоугольный.

Схема синхронизации осуществляет прием тактового сигнала с одного из дифференциальных входов: CLKP/CLKM, CLKDP/CLKDM и обеспечивает формирование тактирующих импульсов для остальных блоков микросхемы. Выбор источника тактового сигнала осуществляется подачей логического уровня на вход CSEL.

#### 3.1. Режим синтеза гармонического сигнала

В режиме синтеза гармонического сигнала аккумулятор частоты не используется.

Аккумулятор фазы увеличивает свое значение на величину, записанную в регистры  $\underline{\text{CHx dPhy L}}$  (разряды [15:0]),  $\underline{\text{CHx dPhy M}}$  (разряды [31:16]),  $\underline{\text{CHx dPhy M}}$  (разряды [47:32]), где x – номер канала (1 или 2), а y – номер профиля (0-63), с тактовой частотой ЦАП. Таким образом, значение выходной частоты определяется

соотношением:

$$F_{out} = \frac{F_{\underline{H}} * 2^{32} + F_{\underline{M}} * 2^{16}}{2^{48}} + F_{\underline{L}} * F_{clk}$$

,

где:

F<sub>out</sub> — синтезируемая частота,

F<sub>clk</sub> — тактовая частота ЦАП,

$F_H = Chx_dPhy_H$ ,

$F_M = Chx_dPhy_M$ ,

$F_L = Chx_dPhy_L.$

Значение аккумулятора фазы складывается с выходом генератора шума (если разрешено битом **pdith** регистра <u>ROUTE</u>) и значением в регистре <u>CHx\_Py</u>, после чего подается на вход преобразователя фаза-амплитуда.

Выходное значения с преобразователя фаза-амплитуда умножается на значение в регистре <a href="CHx\_Muly">CHx\_Muly</a>, затем к нему прибавляется значение <a href="CHx\_Offsety">CHx\_Offsety</a>.

Вычисленное значение передается в выходной маршрутизатор, где оно либо предварительно складывается с выходом другого канала, либо непосредственно передается соответствующий ЦАП, что определяется полем **sum** регистра <u>ROUTE</u>.

Перед подачей на ЦАП, рассчитанное значение амплитуды суммируется с выходом генератора амплитудного шума (если разрешено установкой бита **adith** регистра <u>ROUTE</u>). Также происходит ограничение разрядности с 12 до 10 бит.

Значения частоты, фазы, амплитуды и постоянного смещения записываются в соответствующие регистры  $CHx_dPhy_L$ ,  $CHx_dPhy_M$ ,  $CHx_dPhy_H$ ,  $CHx_Py$ ,  $CHx_Muly$ ,  $CHx_Offsety$  соответственно профиля y независимо для каждого канала x. Выбор рабочего профиля осуществляется записью его номера (0-63) в поля  $Pr_1$  и  $Pr_2$  регистра  $SEL_REG_{DR}$  для 1 и 2 канала соответственно.

# 3.2. Режим модуляции

Работа синтезатора в режиме модуляции аналогична работе в режиме гармонического синтеза.

Модуляция осуществляется путем переключения между двумя и более заранее запрограммированными профилям записью в регистр <u>SEL\_REG</u>. Вид модуляции (FM, PM, AM, QAM и т.д.) определяется содержимым соответствующих профилей.

Также переключение активного профиля может осуществляться подачей кода с его номером на входы SEL при установленном бите SEL\_IE регистра SYNC. Считывание состояния SEL происходит по положительному фронту внутренней тактовой частоты. Эту частоту можно вывести на вывод CSYNC, установив бит CSYNC\_OE регистра SYNC в «1». Задержка управляющего воздействия от положительного фронта внутренней тактовой частоты до выхода ЦАП составляет 63 периода частоты дискретизации ЦАП.

Возможно программировать неактивный профиль «на лету», что дает практически неограниченный выбор типов и режимов модуляции.

Для уменьшения нежелательного расширения спектра синтезируемого сигнала при переключении профилей, имеется возможность «плавного» изменения параметров модуляции. Суть ее состоит в фильтрации параметров модуляции фильтром с импульсной характеристикой, близкой к гауссовой. Длина импульсной характеристики задается регистром  $\underline{\text{CHx TSW}}$  независимо для каждого канала. При  $\underline{\text{tsw}}>0$  интервал между последовательными переключениями параметров модуляции (профилей) должен составлять не менее  $2^{\underline{\text{tsw}}+4}+8$  тактов ЦАП.

#### 3.3. Режим синтеза ЛЧМ сигнала

Цикл формирования ЛЧМ сигнала содержит 4 стадии:

- **ñ** В стадии 1 происходит приращение частоты с шагом dF1 за такт;

- **ñ** В стадии 2 частота сигнала остается неизменной либо имеет нулевое значение (постоянная фаза);

- **ñ** В стадии 3 происходит приращение частоты с шагом dF2 за такт;

- **ñ** В стадии 4 частота сигнала остается неизменной либо имеет нулевое значение (постоянная фаза);

Значения dF1, dF2 задаются регистрами <u>CHx LS dFq1 L(M, H)</u>, <u>CHx LS dFq2L(M, H)</u> соответственно. Приращение частоты задается в дополнительном коде, т.е. может быть как положительным, так и отрицательным.

Длительность каждой стадии задается независимо регистрами <u>CHx\_LS\_TPH1</u> - <u>CHx\_LS\_TPH4</u> соответственно, с дискретностью 4 такта частоты дискретизации ЦАП. При тактовой частоте 1 ГГц, максимальная длительность каждой стадии составляет приблизительно 78 часов.

В стадиях 2 и 4 выходной сигнал может быть отключен установкой в «0» бит s2\_on, s4\_on регистра CHx\_LS\_CTR.

Запуск цикла формирования ЛЧМ сигнала производится записью «1» в биты LS1\_start, LS2\_start регистра CLR для соответствующих каналов.

В начале стадии 1 ЛЧМ, если установлен бит <u>CHx LS CTR.frq reset 1</u>, начальное значение частоты берется из регистра <u>CHx LS F1</u> соответствующего канала. В начале стадии 3 ЛЧМ, если установлен бит <u>CHx\_LS CTR.frq reset\_3</u>, начальное значение частоты берется из регистра <u>CHx\_LS F2</u> соответствующего канала.

Если установлен бит auto регистра  $CHx_LS_CTR$ , по окончании стадии 4 снова начинается формирование стадии 1 в соответствующем канале.

Остановка формирования ЛЧМ производится записью «1» в биты LSx\_stop регистра <u>CLR</u>. При этом происходит немедленный переход к 4 стадии, в которой синтезатор остается неограниченное время.

Также немедленный переход к началу стадии 1-4 ЛЧМ можно осуществить записью регистра <u>SEL\_REG</u> либо аппаратно подачей положительного фронта на соответствующие выводы <u>SEL</u>.

## 3.3.1. Режим коррекции

Бит corr\_enable регистра CHx\_LS\_CTR включает частотно-зависимую коррекцию фазы, амплитуды и постоянного смещения синтезируемого сигнала в режиме ЛЧМ. Старшие 16 бит нижней частоты корректируемого диапазона задаются регистром CHx\_LS\_CRFMIN. Поле CHx\_LS\_CTR.corr\_fscale задает диапазон частот  $\Delta$ F, в котором происходит коррекция:

$$\Delta F = 63/64 * F_{CLK}/2^{corr\_fscale}$$

Параметры коррекции для частоты  $F_0$ =CHx\_LS\_CRFMIN\* $F_{CLK}/2^{16}$  берутся из профиля 0, для частоты  $F_0$ + $\Delta F$  — из профиля 63. Параметры в остальных профилях соответствуют частотам F= $F_0$ + $\Delta F$ \*n/64, где 05n563 — номер профиля.

Значения параметров сигнала, соответствующие промежуточным частотам, вычисляются методом линейной интерполяции.

При отключенной коррекции, параметры фазы, амплитуды и постоянного смещения синтезируемого сигнала берутся из профиля с номерами 1, 2, 3, 0 для стадий 1-4 соответственно.

# 4. ВЫВОДЫ БИС

# 4.1. Назначение выводов

Таблица 1. Назначение выводов БИС

| Наименование Тип  |                       | Описание                                                |    |  |

|-------------------|-----------------------|---------------------------------------------------------|----|--|

| Сигналы компарато | ра                    |                                                         | •  |  |

| CMP_INP           | AI                    | Вход СМР положительный                                  | 1  |  |

| CMP_INM           | AI                    | Вход СМР отрицательный                                  |    |  |

| CMP_OP            | 0                     | Выход СМР положительный                                 | 1  |  |

| CMP_OM            | 0                     | Выход СМР отрицательный                                 | 1  |  |

| Тактовые сигналы  |                       | •                                                       |    |  |

| CLKP              | CI                    | Вход тактовой частоты положительный                     | 1  |  |

| CLKM              | CI                    | Вход тактовой частоты отрицательный                     | 1  |  |

| CLKDP             | CI                    | Альтернативный вход тактовой частоты положительный      | 1  |  |

| CLKDM             | CI                    | Альтернативный вход тактовой частоты отрицательный      | 1  |  |

| Сигналы последова | тельного порт         | а управления (SPI-интерфейс)                            |    |  |

| SDI               | I                     | Вход данных последовательного порта управления          | 1  |  |

| SDO               | О                     | Выход данных последовательного порта управления         | 1  |  |

| SCK               | I                     | Тактовый сигнал сопровождения последовательных данных.  | 1  |  |

| SCSn              | I                     | «Выбор кристалла» последовательного порта управления    | 1  |  |

| SSCSn             | 0                     | Сигнал SCSn, пересинхронизированный сигналом CSYNC      | 1  |  |

| Сигналы параллель | ного порта <b>у</b> п |                                                         |    |  |

| WRn               | I                     | Строб разрешения записи по параллельному порту          | 1  |  |

| RDn               | I                     | Строб разрешения чтения по параллельному порту          | 1  |  |

| CSn               | I                     | Сигнал выбора кристалла                                 | 1  |  |

| ADR               | I                     | Шина адреса параллельного порта                         | 1  |  |

| DATA              | IO                    | Шина данных параллельного порта                         | 16 |  |

| Прочие сигналы    | 10                    | птина данных наразнельного порта                        | 10 |  |

| IREF1             | AI                    | Опорный ток ЦАП1                                        | 1  |  |

| IREF2             | AI                    | Опорный ток ЦАП2                                        | 1  |  |

| OUTP1             | AO                    | Выход ЦАП1 положительный                                | 1  |  |

| OUTM1             | AO                    | Выход ЦАП1 отрицательный                                | 1  |  |

| OUTP2             | AO                    | Выход ЦАП1 огрицательный                                | 1  |  |

| OUTM2             | AO                    | Выход ЦАП2 отрицательный                                | 1  |  |

| RSTn              | I                     | Сигнал аппаратного сброса                               | 1  |  |

| CSYNC             | IO                    | В режиме «ведущий» - выход тактовой частоты ЦАП,        | 1  |  |

| CSTNC             | 10                    | деленной на 4.                                          | 1  |  |

|                   |                       | В режиме «ведомый» - вход синхронизации.                |    |  |

| CSEL              | I                     | Выбор источника тактовой частоты.                       | 1  |  |

| SEL1              | IO                    | Выбор профиля синтеза для 1 канала, LINK-порт,          | 6  |  |

| SELI              |                       | статус/управление ЛЧМ                                   | 0  |  |

| SEL2              | IO                    | Выбор профиля синтеза для 2 канала, статус/управление   | 6  |  |

| SELZ              | 10                    | ЛЧМ                                                     | 0  |  |

| Питание           |                       | JI IIVI                                                 |    |  |

| DVDD              | PWR                   | Питание 1.8 В («тихие» цифровые блоки)                  | 2  |  |

| CVDD              | PWR                   | Питание 1.8 В (цифровое ядро)                           | 7  |  |

| PVDD              | PWR                   | Питание 1.8 В (цифровое ядро) Питание 3.3 В (периферия) | 3  |  |

| AVDD              |                       | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \                   | 3  |  |

|                   | PWR<br>PWR            | Питание 3.3 В (аналоговые блоки)                        | 2  |  |

| AVDD2             |                       | Питание 3.3 В (ЦАП1)                                    | 2  |  |

| AVDD2             | PWR                   | Питание 3.3 В (ЦАП2)                                    |    |  |

| DVDD1             | PWR                   | Питание 1.8 В (ЦАП1)                                    | 1  |  |

| DVDD2             | PWR                   | Питание 1.8 В (ЦАП2)                                    | 1  |  |

| CMP_VDD           | PWR                   | Питание 3.3 В (компаратор)                              | 1  |  |

| CMP_GND           | PWR                   | Земля (компаратор)                                      | 2  |  |

| AGND              | PWR                   | Земля (аналоговые и «тихие» цифровые блоки)             | 11 |  |

| Наименование | Тип | Описание              | кол- |

|--------------|-----|-----------------------|------|

|              |     |                       | во   |

| PGND         | PWR | Земля (периферия)     | 3    |

| CGND         | PWR | Земля (цифровое ядро) | 8    |

| Итого:       |     |                       | 100  |

# 4.2. Расположение выводов

### Таблица 2.Расположение выводов

| №  | Наименование | №  | Наименование | №  | Наименование | №   | Наименование |

|----|--------------|----|--------------|----|--------------|-----|--------------|

| 1  | CVDD         | 26 | AVDD         | 51 | CMP_VDD      | 76  | RDn          |

| 2  | SCK          | 27 | AVDD         | 52 | CMP_OP       | 77  | WRn          |

| 3  | SDI          | 28 | IREF2        | 53 | CMP_OM       | 78  | DATA[0]      |

| 4  | CGND         | 29 | AGND         | 54 | CMP_GND      | 79  | DATA[1]      |

| 5  | SDO          | 30 | AVDD2        | 55 | CGND         | 80  | DATA[2]      |

| 6  | SCSn         | 31 | AVDD2        | 56 | SEL2[0]      | 81  | DATA[3]      |

| 7  | SSCSn        | 32 | AGND         | 57 | SEL2[1]      | 82  | CVDD         |

| 8  | CSn          | 33 | OUTM2        | 58 | SEL2[2]      | 83  | DATA[4]      |

| 9  | PVDD         | 34 | OUTP2        | 59 | SEL2[3]      | 84  | DATA[5]      |

| 10 | RSTn         | 35 | AGND         | 60 | CVDD         | 85  | CGND         |

| 11 | ADR          | 36 | DVDD2        | 61 | CVDD         | 86  | CGND         |

| 12 | PGND         | 37 | IREF1        | 62 | SEL2[4]      | 87  | DATA[6]      |

| 13 | CSEL         | 38 | AGND         | 63 | SEL2[5]      | 88  | DATA[7]      |

| 14 | CVDD         | 39 | AVDD1        | 64 | CGND         | 89  | DATA[8]      |

| 15 | CVDD         | 40 | AVDD1        | 65 | CGND         | 90  | DATA[9]      |

| 16 | DVDD         | 41 | AGND         | 66 | PGND         | 91  | PGND         |

| 17 | AGND         | 42 | OUTM1        | 67 | SEL1[0]      | 92  | DATA[10]     |

| 18 | CLKDP        | 43 | OUTP1        | 68 | SEL1[1]      | 93  | DATA[11]     |

| 19 | CLKDM        | 44 | AGND         | 69 | PVDD         | 94  | PVDD         |

| 20 | AGND         | 45 | DVDD1        | 70 | SEL1[2]      | 95  | DATA[12]     |

| 21 | AVDD         | 46 | AGND         | 71 | SEL1[3]      | 96  | DATA[13]     |

| 22 | AGND         | 47 | DVDD         | 72 | CGND         | 97  | DATA[14]     |

| 23 | CLKM         | 48 | CMP_GND      | 73 | SEL1[4]      | 98  | DATA[15]     |

| 24 | CLKP         | 49 | CMP_INM      | 74 | SEL1[5]      | 99  | CGND         |

| 25 | AGND         | 50 | CMP_INP      | 75 | CVDD         | 100 | CSYNC        |

# 4.3. Назначение выводов SEL в различных режимах

Таблица 3. Назначение выводов SEL в различных режимах

| Состояни | е управляющего       | бита                 |             | Режим работы                                                                                                              |

|----------|----------------------|----------------------|-------------|---------------------------------------------------------------------------------------------------------------------------|

| LINK.on  | CH1_LS_CTR.<br>LS_on | CH2_LS_CTR.<br>LS_on | SYNC.SEL_IE |                                                                                                                           |

| 0        | 0                    | 0                    | 1           | SEL1, SEL2 выбирают активный профиль в каналах 1 и 2 соответственно.                                                      |

| 0        | 0                    | 1                    | 1           | SEL1 выбирает активный профиль канала 1, SEL2[3:0] управляют запуском стадий ЛЧМ в канале 2.                              |

| 0        | 1                    | 0                    | 1           | SEL2 выбирает активный профиль канала 2, SEL1[3:0] управляют запуском стадий ЛЧМ в канале 1.                              |

| 0        | 1                    | 1                    | 1           | SEL1[3:0] и SEL2[3:0] управляют запуском стадий ЛЧМ в каналах 1 и 2 соответственно                                        |

| 1        | 0                    | 0                    | X           | SEL1[3:0] – данные LINK-порта (LDAT),<br>SEL1[4] – LCLK,<br>SEL1[5] – LACK.                                               |

| 1        | 0                    | 1                    | 1           | SEL1[3:0] — данные LINK-порта (LDAT), SEL1[4] — LCLK, SEL1[5] — LACK, SEL2[3:0] управляют запуском стадий ЛЧМ в канале 2. |

# 5. ВНУТРЕННЕЕ АДРЕСНОЕ ПРОСТРАНСТВО.

Внутреннее адресное пространство содержит управляющие и статусные 16 разрядные регистры. Доступ во внутреннее адресное пространство возможен либо через параллельный порт, либо через последовательный порт управления.

### 5.1. Адресное пространство регистров управления DDS.

Таблица 4. Адресное пространство регистров управления DDS.

| Адрес | Сброс | Тип              | Имя            | Назначение                                              |

|-------|-------|------------------|----------------|---------------------------------------------------------|

| 0000  | 0000  | $\mathbf{W}^{1}$ | SWRST          | Регистр программного сброса                             |

| 0001  | 0201  | $R^2$            | DEVID          | Идентификатор устройства, только чтение                 |

| 0002  | 0000  | $RW^3$           | SEL REG        | Выбор активного профиля синтеза                         |

| 0003  | 0003  | RW               | CTR            | Регистр управления                                      |

| 0004  | 4800  | RW               | SYNC           | Управление синхронизацией                               |

| 0005  | 0000  | W                | CLR            | Очистка аккумуляторов фазы, запуск и остановка ЛЧМ      |

| 0006  | 0000  | RW               | <u>LINK</u>    | Управление LINK-интерфейсом                             |

| 0007  | 0000  | RW               | ROUTE          | Управление потоком данных и рандомизацией               |

| 0008  | XXXX  | RW               | TC L           | Делитель чиповой скорости, биты [15:0]                  |

| 0009  | XXXX  | RW               | TC H           | Делитель чиповой скорости, биты [31:16]                 |

| 00E0  | 0000  | W                | T_CAPTURE      | Отладочный регистр: фиксация текущего состояния каналов |

|       |       |                  |                | для последующего считывания.                            |

| 00E1  | XXXX  | R                | T_SEL_STATE    | Отладочный регистр: текущее состояние выводов SEL       |

| 00E2  | XXXX  | R                | T_E_SEL        | Отладочный регистр: эффективный SEL                     |

| 1000: | XXXX  |                  | CH1_*          | Регистры первого канала                                 |

| 14F3  |       |                  |                |                                                         |

| 1000  | 0000  | RW               | CH1 LS CTR     | Управление синтезом ЛЧМ.                                |

| 1001  | 0000  | RW               | CH1 LS CRFMIN  | Нижняя граница корректируемого диапазона частот         |

| 1002  | 0000  | RW               | CH1 TSW        | Управление временем переключения параметров синтеза.    |

| 1010  | XXXX  | RW               | CH1 LS TPH1 L  | Регистр длительности 1-ой фазы ЛЧМ-сигнала [15:0]       |

| 1011  | XXXX  | RW               | CH1_LS_TPH1_M  | Регистр длительности 1-ой фазы ЛЧМ-сигнала [31:16]      |

| 1012  | XXXX  | RW               | CH1_LS_TPH1_H  | Регистр длительности 1-ой фазы ЛЧМ-сигнала [45:32]      |

| 1014: | XXXX  | RW               | CH1 LS TPH2 L( | Регистры длительности 2-ой фазы ЛЧМ-сигнала             |

| 1016  |       |                  | <u>M, H)</u>   | (аналогично регистрам длительности 1 фазы ЛЧМ-сигнала)  |

| 1018: | XXXX  | RW               | CH1_LS_TPH3_L( | Регистры длительности 3-й фазы ЛЧМ-сигнала              |

| 101A  |       |                  | <u>M, H)</u>   | (аналогично регистру длительности 1 фазы ЛЧМ-сигнала)   |

| 101C: | XXXX  | RW               | CH1_LS_TPH4_L( | Регистры длительности 4-й фазы ЛЧМ-сигнала              |

| 101E  |       |                  | <u>M, H)</u>   | (аналогично регистру длительности 1 фазы ЛЧМ-сигнала)   |

| 1020  | XXXX  |                  | CH1 LS F1 L    | Регистр начальной частоты ЛЧМ 1 [15:0]                  |

| 1021  | XXXX  |                  | CH1 LS F1 M    | Регистр начальной частоты ЛЧМ 1 [31:16]                 |

| 1022  | XXXX  |                  | CH1 LS F1 H    | Регистр начальной частоты ЛЧМ 1 [47:32]                 |

| 1024  | XXXX  |                  | CH1 LS F2 L    | Регистр начальной частоты ЛЧМ 2 [15:0]                  |

| 1025  | XXXX  |                  | CH1 LS F2 M    | Регистр начальной частоты ЛЧМ 2 [31:16]                 |

| 1026  | XXXX  |                  | CH1 LS F2 H    | Регистр начальной частоты ЛЧМ 2 [47:32]                 |

| 1030  | XXXX  |                  | CH1 LS Ph1     | Регистр начальной фазы ЛЧМ 1                            |

| 1031  | XXXX  |                  | CH1 LS Ph2     | Регистр начальной фазы ЛЧМ 2                            |

| 1040  | XXXX  |                  | CH1 LS dF1 L   | Регистр приращения частоты 1 [15:0]                     |

| 1041  | XXXX  |                  | CH1_LS dF1_M   | Регистр приращения частоты 1 [31:16]                    |

| 1042  | XXXX  |                  | CH1_LS dF1_H   | Регистр приращения частоты 1 [47:32]                    |

| 1044: | XXXX  | RW               | CH1_LS_dF2_L   | Регистры приращения частоты 2                           |

| 1046  | 0007  |                  | (M,H)          | (аналогично регистрам приращения частоты 1)             |

| 1300  | 0000  | W                | CH1 dPh all L  | Запись приращения фазы [15:0] во все профили            |

| 1301  | 0000  | W                | CH1 dPh all M  | Запись приращения фазы [31:16] во все профили           |

<sup>1</sup> W — регистр только для записи. При чтении возвращается 0.

<sup>2</sup> R — регистр только для чтения. Запись игнорируется.

<sup>3</sup> RW — регистр можно писать и читать

| Адрес  | Сброс | Тип | Имя            | Назначение                                          |

|--------|-------|-----|----------------|-----------------------------------------------------|

| 1302   | 0000  | W   | CH1_dPh_all_H  | Запись приращения фазы [47:32] во все профили       |

| 1304   | 0000  | W   | CH1_P_all      | Запись смещения фазы во все профили                 |

| 1305   | 0000  | W   | CH1_Mul_all    | Запись коэффициента усиления во все профили         |

| 1306   | 0000  | W   | CH1_Offset_all | Запись постоянного смещения во все профили          |

| 1400   | XXXX  | RW  | CH1_dPh0_L     | Регистр приращения фазы [15:0], профиль 0           |

| 1401   | XXXX  | RW  | CH1_dPh0_M     | Регистр приращения фазы [31:16], профиль 0          |

| 1402   | XXXX  | RW  | CH1_dPh0_H     | Регистр приращения фазы [47:32], профиль 0          |

| 1404   | XXXX  | RW  | <u>CH1_P0</u>  | Регистр управления фазой, профиль 0                 |

| 1405   | XXXX  | RW  | CH1_Mul0       | Регистр управления амплитудой, профиль 0            |

| 1406   | XXXX  | RW  | CH1_Offset0    | Регистр упр. смещением выходного сигнала, профиль 0 |

| 1410:  | XXXX  | RW  | CH1_dPy_L(M,H) | Параметры профилей 1-63                             |

| 17F6   |       |     | CH1_Py         |                                                     |

|        |       |     | CH1 Muly       |                                                     |

|        |       |     | CH1 Offsety    |                                                     |

| 1800:1 |       |     |                | Отладочные регистры первого канала                  |

| 8FF    |       |     |                |                                                     |

| 1800   |       | R   | CH1_T_dPh_L    | Приращение фазы [15:0]                              |

| 1801   | XXXX  | R   | CH1_T_dPh_M    | Приращение фазы [31:16]                             |

| 1802   |       | R   | CH1_T_dPh_H    | Приращение фазы [47:32]                             |

| 1804   |       | R   | CH1_T_P        | Смещение фазы                                       |

| 1805   |       | R   | CH1_T_Mul      | Коэффициент умножения                               |

| 1806   |       | R   | CH1_T_Offset   | Постоянное смещение                                 |

| 1808   | XXXX  | R   | CH1_T_SEL      | Номер активного профиля                             |

| 1810   | XXXX  | R   | CH1_T_out1     | Выход 1 подканала                                   |

| 1811   | XXXX  | R   | CH1_T_out2     | Выход 2 подканала                                   |

| 1812   |       | R   | CH1_T_out3     | Выход 3 подканала                                   |

| 1813   | XXXX  | R   | CH1_T_out4     | Выход 4 подканала                                   |

| 2000:  | XXXX  |     | CH2_*          | Регистры второго канала                             |

| 2813   |       |     |                | (аналогично первому каналу)                         |

Зарезервированные поля и регистры читаются нулями. Запись в них игнорируется.

#### **5.2. SWRST**

Запись в регистр числа 007816 вызывает программный сброс, полностью аналогичный аппаратному. При чтении возвращается '0'

#### **5.3. DEVID**

Регистр 16-бит идентификатора типа устройства. Доступен только по чтению.

# **5.4. SEL\_REG**

Выбор текущего профиля синтеза.

| Бит     | Имя поля  | Назначение                                             |  |  |  |

|---------|-----------|--------------------------------------------------------|--|--|--|

| [15:14] | LS2_stage | Запись: запуск соответствующей стадии ЛЧМ во 2 канале; |  |  |  |

|         |           | Чтение: текущая стадия ЛЧМ во 2 канале                 |  |  |  |

| [13:6]  | Pr_2      | Режим не-ЛЧМ, чтение, запись:                          |  |  |  |

|         |           | Текущий профиль синтеза во 2 канале;                   |  |  |  |

| [7:6]   | LS1_stage | Запись: запуск соответствующей стадии ЛЧМ в 1 канале;  |  |  |  |

|         |           | Чтение: текущая стадия ЛЧМ в 1 канале                  |  |  |  |

| [5:0]   | Pr_1      | Режим не-ЛЧМ, чтение, запись:                          |  |  |  |

|         |           | Текущий профиль синтеза в 1 канале                     |  |  |  |

#### 5.5. CTR

Общее управление режимами работы микросхемы.

| Бит    | Имя поля | Назначение                                                                                                                                                                                   |  |  |  |

|--------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 15     | res      | Зарезервировано                                                                                                                                                                              |  |  |  |

| 14     | CMP_on   | 1: включение компаратора                                                                                                                                                                     |  |  |  |

| 13     | DAC2_on  | 1: вкл. ЦАП 2                                                                                                                                                                                |  |  |  |

| 12     | DAC1_on  | 1: вкл. ЦАП 1                                                                                                                                                                                |  |  |  |

| [11:5] | res      | Зарезервировано                                                                                                                                                                              |  |  |  |

| [4:0]  | cmx      | Коэффициент деления тактового сигнала. При CSEL=0, коэффициент деления со входов CLKP, CLKM: 0: 1:1; 1: 1:2; 3: 1:4. При CSEL=1, коэффициент деления частоты со входов CLKDP, CLKDM равен 1. |  |  |  |

#### **5.6. SYNC**

Управление режимами синхронизации.

| Бит | Имя поля   | Назначение                                                                                                                                                                                                                                 |  |  |

|-----|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 15  | res        | Зарезервировано                                                                                                                                                                                                                            |  |  |

| 14  | CSYNC_OE   | Разрешение выдачи на CSYNC частоты дискретизации, деленной на 4 (8)                                                                                                                                                                        |  |  |

| 13  | CSYNC_IE   | Разрешение использования входного сигнала CSYNC для синхронизации                                                                                                                                                                          |  |  |

| 12  | res        | Зарезервировано                                                                                                                                                                                                                            |  |  |

| 11  | CSYNC_DIV  | Разрешение дополнительного деления частоты CSYNC на 2 перед выдачей на CSYNC (т.е. в итоге частота дискретизации делится на 8).                                                                                                            |  |  |

| 10  | SPI_master | 1: разрешение выхода SSCSn                                                                                                                                                                                                                 |  |  |

| 9   | SYNC_del   | 1: дополнительная задержка входного сигнала CSYNC на $0.5$ нс. Для случаев, когда не соблюдается $t_{sucsc}$                                                                                                                               |  |  |

| 8   | SEL_IE     | В не-ЛЧМ режиме: 0: активный профиль выбирается записью в регистр SEL_REG; 1: активный профиль выбирается аппаратно сигналами SEL. В режиме ЛЧМ: 1: положительный фронт на входах SEL[0] – SEL[3] запускает стадию 1-4 ЛЧМ соответственно. |  |  |

| Бит   | Имя поля       | Назначение                                                          |

|-------|----------------|---------------------------------------------------------------------|

| 7     | SEL_OE         | 1: сигналы SEL являются выходными в не-ЛЧМ режиме при отключенном   |

|       |                | LINK-интерфейсе и индицируют номер активного профиля.               |

|       |                | В режиме ЛЧМ, SEL[5:4] являются выходными и индицируют текущую      |

|       |                | стадию ЛЧМ.                                                         |

| [6:5] | SYNC_Phase     | Фаза синхронизации. Задержка тактовой частоты вычислительного ядра  |

|       |                | относительно входного сигнала CSYNC, в тактах частоты дискретизации |

|       |                | ЦАП.                                                                |

| [4:3] | SYNC_Out_Phase | Задержка выходного сигнала CSYNC, тактов ЦАП.                       |

| [2:0] | res            | Зарезервировано                                                     |

# 5.7. CLR

Управление очисткой аккумуляторов фазы и запуск/остановка ЛЧМ.

| Бит | Имя поля   | Назначение                                                               |

|-----|------------|--------------------------------------------------------------------------|

| 11  | bist_clr   | Очистка регистров самотестирования                                       |

| 10  | link_clr   | Очистка очередей данных LINK-интерфейса                                  |

|     | link_start | Сброс Тс и запуск приема данных с LINK-порта для режима внутренней       |

| 9   |            | синхронизации                                                            |

| 8   | link_stop  | Остановка приема данных с LINK-порта для режима внутренней синхронизации |

| 7   | LS2_stop   | Остановка (переход к стадии 4) ЛЧМ последовательности во 2 канале        |

| 6   | LS1_stop   | Остановка (переход к стадии 4) ЛЧМ последовательности в 1 канале         |

| 5   | LS2_start  | Запуск (переход к стадии 1) ЛЧМ последовательности во 2-ом канале        |

| 4   | LS1_start  | Запуск (переход к стадии 1) ЛЧМ последовательности в 1-ом канале         |

| 3   | Clr_fq2    | Установка аккумулятора частоты 2-канала в значение CH2_LS_F1             |

| 2   | Clr_fq1    | Установка аккумулятора частоты 1-канала в значение CH1_LS_F1             |

| 1   | Clr_ph2    | Очистка аккумулятора фазы 2-канала                                       |

| 0   | Clr_ph1    | Очистка аккумулятора фазы 1-канала                                       |

# **5.8. LINK**

Управление LINK-интерфейсом.

| Бит    | Имя поля | Назначение                                                                                       |

|--------|----------|--------------------------------------------------------------------------------------------------|

| [15:5] | res      | Зарезервировано                                                                                  |

| [4:3]  | clk_mode | Режим тактирования.                                                                              |

|        |          | 0: длительность символа равна 4*T <sub>clk</sub> *(TC_H*2 <sup>16</sup> +TC_L);                  |

|        |          | 1: длительность символа равна 4*T <sub>clk</sub> *2 <sup>32</sup> /(TC_H*2 <sup>16</sup> +TC_L); |

|        |          | 3: внешняя синхронизация. Переключение профилей происходит по                                    |

|        |          | положительному фронту на SEL2[0];                                                                |

|        |          | Т <sub>сlk</sub> — период тактовой частоты ЦАП                                                   |

| [2:1]  | res      | Зарезервировано                                                                                  |

| 0      | on       | 1 – включение LINK-интерфейса. В этом режиме линии SEL1 используются под                         |

|        |          | LINK порт.                                                                                       |

|        |          | В режиме LINK.on=1, регистры с адресами >=0x1000 недоступны на запись.                           |

#### **5.9. ROUTE**

Управление маршрутизацией сигнала к ЦАП и амплитудным выбеляющим шумом.

| Бит   | Имя поля | Назначение                                                                 |

|-------|----------|----------------------------------------------------------------------------|

| 7     | pdith2   | 1 = вкл. рандомизации фазы 2 канала.                                       |

| 6     | pdith1   | 1 = вкл. рандомизации фазы 1 канала.                                       |

| [5:4] | adith1   | 0: рандомизация амплитуды перед ограничением разрядности в 1 канале        |

|       |          | выключена;                                                                 |

|       |          | 1: амплитуда шума ½*LSB ЦАП;                                               |

|       |          | 2: зарезервировано;                                                        |

|       |          | 3: амплитуда шума 8*LSB ЦАП.                                               |

| [3:2] | adith2   | То же для канала 2. При этом в режиме adith1=adith2=3 гарантируется, что   |

|       |          | мгновенные значения выбеляющего шума для двух каналов равны по модулю и    |

|       |          | противоположны по знаку, т.е. их сумма равна нулю.                         |

| [1:0] | sum      | Маршрутизация данных от каналов синтеза к ЦАП.                             |

|       |          | 0: сигнал каждого канала поступает на «свой» ЦАП                           |

|       |          | 1: сигнал 1 канала подается на оба ЦАПа.                                   |

|       |          | 2: сигнал 2 канала подается на оба ЦАПа.                                   |

|       |          | 3: сигналы каналов суммируются перед ограничением разрядности и подаются   |

|       |          | на оба ЦАПа.                                                               |

|       |          | Режим суммирования позволяет при параллельном соединении выходов ЦАП       |

|       |          | увеличить эффективную разрядность на 1 бит, а добавление при этом          |

|       |          | противофазного шума ( adith1=adith2=3) позволяет снизить влияние глитчей и |

|       |          | дифференциальной нелинейности ЦАП.                                         |

#### 5.10. CH*x*\_TSW

Длина импульсной характеристики гауссового фильтра, канал х.

| Бит    | Имя поля | Назначение                                                                      |

|--------|----------|---------------------------------------------------------------------------------|

| [15:3] | res      | Зарезервировано                                                                 |

|        |          | tsw=0: Фильтрация отключена;                                                    |

| [2:0]  | tsw      | tsw>0: 2 <sup>tsw+4</sup> - время переключения (длина импульсной характеристики |

|        |          | фильтра) в тактах ЦАП.                                                          |

# **5.11.** CH*x*\_dPhy\_L

Приращение фазы, канал х, профиль у, младшие 16 разрядов

| Бит    | Имя поля | Назначение                                          |

|--------|----------|-----------------------------------------------------|

| [15:0] | value    | Приращение фазы, разряды [15:0], канал х, профиль у |

# 5.12. CHx\_dPhy\_M

Приращение фазы, канал x, профиль y, разряды [31:16]

| Бит    | Имя поля | Назначение                                           |

|--------|----------|------------------------------------------------------|

| [15:0] | value    | Приращение фазы, разряды [31:16], канал х, профиль у |

# **5.13.** CH*x*\_dPhy\_H

Приращение фазы, канал х, профиль у, старшие 16 разрядов

| Бит    | Имя поля | Назначение                                           |

|--------|----------|------------------------------------------------------|

| [15:0] | value    | Приращение фазы, разряды [47:32], канал х, профиль у |

#### 5.14. CHx\_Py

Установка сдвига фазы в профиле у канала x.

| Бит    | Имя поля | Назначение                                                                                                                |

|--------|----------|---------------------------------------------------------------------------------------------------------------------------|

| [15:0] |          | Смещение фазы синтезируемого сигнала ( $\Phi$ ). value — двоично-дополнительное целое. $\Phi = \pi^* \text{value}/2^{15}$ |

#### 5.15. CH*x*\_Muly

Установка амплитуды выходного сигнала в профиле у канала x.

| Бит    | Имя поля | Назначение                                                             |

|--------|----------|------------------------------------------------------------------------|

| [15:3] | mul      | Амплитуда синтезируемого сигнала (A). $A=mul/2^{12}$ , $mul-$ двоично- |

|        |          | дополнительное целое                                                   |

| [2:0]  | res      | Зарезервировано                                                        |

#### 5.16. CHx\_Offsety

Постоянное смещение синтезируемого сигнала в профиле y канала x.

| Бит    | Имя поля | Назначение                                         |

|--------|----------|----------------------------------------------------|

| [15:4] | offset   | Постоянное смещение. Двоично-дополнительное целое. |

| [3:0]  | res      | Зарезервировано                                    |

# 5.17. CHx\_dPh\_all\_L

Запись 16 младших разрядов приращения фазы во все профили канала x. При чтении возвращается значение 0.

| P      | - v - F v - v - v - v - v - v - v - v - v |                                                        |  |

|--------|-------------------------------------------|--------------------------------------------------------|--|

| Бит    | Имя поля                                  | Назначение                                             |  |

| [15:0] | value                                     | Приращение фазы, разряды [15:0], канал х, все профили. |  |

# 5.18. CHx\_dPh\_all\_M

Запись разрядов [31:16] приращения фазы во все профили канала x. При чтении возвращается значение 0.

| Бит    | Имя поля | Назначение                                              |

|--------|----------|---------------------------------------------------------|

| [15:0] | value    | Приращение фазы, разряды [31:16], канал х, все профили. |

#### 5.19. CHx\_dPh\_all\_H

Запись 16 старших разрядов приращения фазы во все профили канала x. При чтении возвращается значение 0.

| Бит    | Имя поля | Назначение                                              |

|--------|----------|---------------------------------------------------------|

| [15:0] | value    | Приращение фазы, разряды [47:32], канал х, все профили. |

#### 5.20. CHx\_P\_all

Запись сдвига фазы во все профили канала х. При чтении возвращается значение 0.

| Бит    | Имя поля | Назначение                                                                                                     |

|--------|----------|----------------------------------------------------------------------------------------------------------------|

| [15:0] | Waliie   | Смещение фазы синтезируемого сигнала. value — двоично-дополнительное целое. $\Phi = \pi^* \text{value}/2^{15}$ |

# 5.21. CHx\_Mul\_all

Запись амплитуды выходного сигнала во все профили канала x. При чтении возвращается значение 0.

| Бит    | Имя поля | Назначение                                                                       |

|--------|----------|----------------------------------------------------------------------------------|

| [15:3] | mul      | Амплитуда синтезируемого сигнала. $A=mul/2^{12}$ , $mul-$ двоично-дополнительное |

|        |          | целое                                                                            |

| [2:0]  | res      | Зарезервировано                                                                  |

# 5.22. CHx\_Offset\_all

Запись постоянного смещения синтезируемого сигнала во все профили канала x. При чтении возвращается значение 0.

| Бит   | Имя поля | Назначение                                         |

|-------|----------|----------------------------------------------------|

| 15:4] | offset   | Постоянное смещение. Двоично-дополнительное целое. |

| [3:0] | res      | Зарезервировано                                    |

# **5.23.** CH*x*\_LS\_CTR

| Бит   | Имя поля    | Назначение                                                                |

|-------|-------------|---------------------------------------------------------------------------|

| 15    | LS_on       | 1: включение режима ЛЧМ.                                                  |

| 14    | PA_bypass   | 1: отключение преобразования фаза/амплитуда                               |

| 13    | frq_reset_3 | "1": установка частоты в начале стадии 3 в значение CHx_LS_F2.            |

| 12    | frq_reset_1 | "1": установка частоты в начале стадии 1 в значение CHx_LS_F1.            |

| 11    | ph_reset_3  | Сброс фазы в CHx_LS_Ph2 в начале стадии 3.                                |

| 10    | ph_reset_1  | Сброс фазы в CHx_LS_Ph1 в начале стадии 1.                                |

| 9     | s2_on       | "0" выключение сигнала во 2-ой стадии.                                    |

| 8     | s4_on       | "0" выключение сигнала в 4-ой стадии.                                     |

| 7     | corr_enable | "1": в ЛЧМ режиме включение кусочно-линейной коррекции сигнала.           |

| 6     | s2_f0       | 1: нулевое приращение фазы в стадии 2                                     |

| 5     | s4_f0       | 1: нулевое приращение фазы в стадии 4                                     |

|       | auto        | Автоповтор ЛЧМ последовательности (переход к стадии 1 по окончании стадии |

| 4     |             | 4).                                                                       |

| [3:0] | corr_fscale | Масштаб диапазона коррекции сигнала. См. 3.3.1.                           |

#### 5.24. CHx\_LS\_CRFMIN

Нижняя граница корректируемого диапазона частот

| Бит    | Имя поля | Назначение                                                                 |

|--------|----------|----------------------------------------------------------------------------|

| [15:0] | value    | Установка нижней границы корректируемого диапазона частот, старшие 16 бит. |

# 5.25. CHx\_LS\_F1(2)\_L(M, H)

Регистры начальной частоты для стадий 1, 3 ЛЧМ.

| - · · · · · · · · · · · · · · · · · · · |          |                                                     |

|-----------------------------------------|----------|-----------------------------------------------------|

| Бит                                     | Имя поля | Назначение                                          |

| [15:0]                                  | value    | Значение частоты, разряды [15:0] ([31:16], [47:32]) |

### 5.26. CHx\_LS\_Ph1(2)

Регистры начальной фазы для стадий 1, 3 ЛЧМ.

| Бит    | Имя поля | Назначение                                                                              |

|--------|----------|-----------------------------------------------------------------------------------------|

| [15:0] | value    | Значение фазы. value – двоично-дополнительное целое. $\Phi = \pi^* \text{value}/2^{15}$ |

# 5.27. CHx\_LS\_dFy\_L

Регистры у канала х приращения частоты для режима ЛЧМ.

| Бит    | Имя поля | Назначение                         |

|--------|----------|------------------------------------|

| [15:0] | value    | Приращение частоты, разряды [15:0] |

#### $5.28. CHx_LS_dFy_M$

Регистры у канала х приращения частоты для режима ЛЧМ.

| Бит    | Имя поля | Назначение                          |

|--------|----------|-------------------------------------|

| [15:0] | value    | Приращение частоты, разряды [31:16] |

# 5.29. CHx\_LS\_dFy\_H

Регистры у канала х приращения частоты для режима ЛЧМ.

|        | ,        | $f 1  \  \                 $        |

|--------|----------|-------------------------------------|

| Бит    | Имя поля | Назначение                          |

| [15:0] | value    | Приращение частоты, разряды [47:32] |

# **5.30.** CH*x*\_LS\_TPH1\_L(M, H)

Длительность 1-ой стадии ЛЧМ

| Бит    | Имя поля | Назначение                                                              |

|--------|----------|-------------------------------------------------------------------------|

| [15:0] | value    | Длительность 1-ой стадии ЛЧМ, Tclk*4. Разряды [15:0] ([31:16], [45:32]) |

# **5.31.** CH*x*\_LS\_TPH2\_L(M, H)

Длительность 2-ой стадии ЛЧМ

| Бит    | Имя поля | Назначение                                                              |

|--------|----------|-------------------------------------------------------------------------|

| [15:0] | value    | Длительность 2-ой стадии ЛЧМ, Tclk*4. Разряды [15:0] ([31:16], [45:32]) |

### **5.32.** CH*x*\_LS\_TPH3\_L(M, H)

Длительность 3-й стадии ЛЧМ

| <u> </u> |          | 1                                                                       |

|----------|----------|-------------------------------------------------------------------------|

| Бит      | Имя поля | Назначение                                                              |

| [15:0]   | value    | Длительность 3-ой стадии ЛЧМ, Tclk*4. Разряды [15:0] ([31:16], [45:32]) |

#### $5.33. CHx_LS_TPH4_L(M, H)$

Длительность 4-й стадии ЛЧМ

| r i e e e e e e e e e e e e e e e e e e |          |                                                                         |  |  |  |  |  |

|-----------------------------------------|----------|-------------------------------------------------------------------------|--|--|--|--|--|

| Бит                                     | Имя поля | Назначение                                                              |  |  |  |  |  |

| [15:0]                                  | value    | Длительность 4-ой стадии ЛЧМ, Tclk*4. Разряды [15:0] ([31:16], [45:32]) |  |  |  |  |  |

# 6. ОПИСАНИЕ ИНТЕРФЕЙСОВ

#### 6.1. Параллельный порт управления DDS.

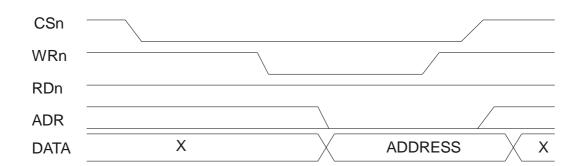

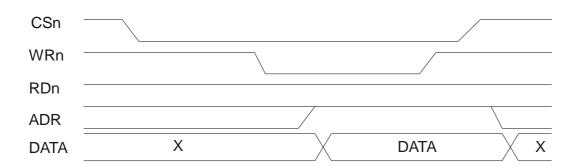

Параллельный интерфейс служит для чтения и записи 16-битных регистров управления ЦВС.

Обмен данными контролируются сигналами выборка кристалла CSn, строб чтения RDn и строб записи WRn.

При использовании параллельного порта на входе SCSn должен присутствовать высокий уровень.

Сигналы CSn, RDn, WRn имеют низкий активный уровень.

Сигал ADR выбирает доступ к адресному регистру (ADR=0), либо к данным (ADR=1).

Передача информации происходит по двунаправленной 16-разрядной шине DATA. Направление передачи определяется сигналом RDn. Низкий уровень разрешает выдачу данных из микросхемы.

Для осуществления доступа к регистру микросхемы, необходимо вначале в адресный регистр записать адрес, по которому будет осуществляться доступ (ADR=0), затем при ADR=1 произвести операцию чтения или записи данных.

Рисунок 6.1. Запись адреса в адресный регистр

Рисунок 6.2. Запись данных

#### 6.2. Линк-порт

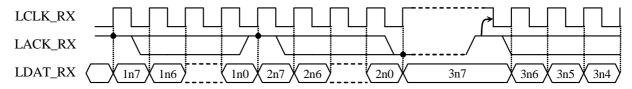

Линк-порт предназначен для осуществления модуляции путем переключения заранее запрограммированных профилей. Линк-порт совместим с 4-разрядным линк-портом ИС SHARC. Управление линк-портом осуществляется с помощью регистра <u>LINK</u>.

Для включения ЛИНК-порта необходимо записать «1» в поле «on» регистра LINK. В этом режиме линии SEL1 получают следующее назначение:

SEL1[3:0]: LDAT (входные данные линк-порта, вход);

SEL1[4]: LCLK (тактовый сигнал, вход);

SEL1[5]: LACK (сигнал подтверждения, выход)

Временные диаграммы работы показаны на рисунке .6.1.

В режиме линк-порта (LINK.on=1), регистры с адресами >=0x1000 недоступны на запись.

#### 6.2.1. Формат данных:

Информационной единицей (символом) является байт (8 бит). Поскольку разрядность физического равна 4 бит, передача одного символа занимает 2 такта LCLK.

Данные передаются старшим значащим полубайтом вперед по фронту сигнала LCLK.

Младшие 6 бит определяют индекс (0-63) профиля формирования сигнала, биты 6 и 7 означают, к какому каналу относятся данные, соответственно 1 и 2. Если установлены оба бита, выбирается заданный профиль одновременно в обоих каналах. Если оба бита сброшены, данные игнорируются без ожидания символьной синхронизации.

Допускается произвольное чередование данных для обоих каналов, однако в любой момент разность количества символов для обоих каналов не должна превышать 16.

Данные передаются блоками по 4 байта. Передача начинается, если сигнал LACK установлен и есть данные для передачи. Если при передаче первого полубайта очередного блока сигнал LACK не установлен, то передача приостанавливается, с сохранением LCLK в 1. После перехода сигнала LACK в 1 передача возобновляется. При отсутствии данных для передачи сигнал LCLK удерживается в 0.

Рисунок 6.3. Временная диаграмма работы LINK-интерфейса.

#### 6.2.2. Управление скоростью

Скорость приема данных может задаваться либо программированием внутреннего счетчик-делителя, либо подачей внешнего тактового сигнала. Выбор режима осуществляется записью в поле «clk\_mode» регистра LINK, а скорость модуляции в режиме внутренней синхронизации задается регистрами TC\_H, TC\_L.

При LINK.LINK\_clk\_mode=3 переключение профилей происходит по положительному фронту сигнала синхронизации SEL2[0].

При значениях LINK.LINK\_clk\_mode, равных 0 или 1, частота синхронизации образуется делением внутренней тактовой частоты.

Для задания режима внутренней синхронизации, в поле clk\_mode регистра LINK необходимо записать значение 0 (режим деления) или 1 (режим умножения). В первом случае, период следования символов будет составлять  $T_{CLK}*4*(TC_H*65536+TC_L)$ , во втором –  $T_{CLK}*4*2^{32}/(TC_H*65536+TC_L)$ .

Здесь T<sub>CLK</sub> -частота дискретизации ЦАП.

Следует выбирать режим внутренней синхронизации, обеспечивающий меньшее отклонение скорости модуляции от номинальной.

#### 6.3. Последовательный порт управления DDS.

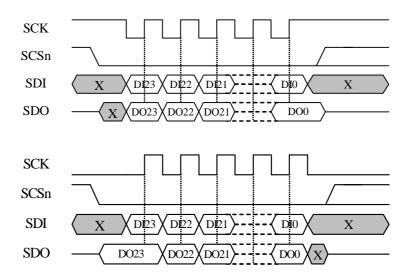

Для управления DDS используется последовательный порт совместимый с интерфейсом SPI. Обращение к регистрам внутреннего адресного пространства осуществляется с помощью 24-битовых команд, подаваемых на вход SDI.

Порт выглядит извне как сдвиговый регистр длиной 24 бита. Входом регистра является SDI, выходом – SDO. Информация в сдвиговый регистр записывается по положительному фронту SCSn. Выполнение команды начинается по положительному фронту SCSn.

Таким образом, значащими информационными являются последние 24 бита, принятые со входа SDI.

Описанная логика работы дает возможность последовательного соединения неограниченного количества микросхем с возможностью синхронного выполнения команд.

При выполнении команды, данные в сдвиговом регистре модифицируется в соответствии с таблицей 6.1.

Длина команды составляет 24 бита. Первые 8 бит содержат код команды, остальные 16 — параметры.

Считывание данных с линии SDI осуществляется по фронту сигнала SCLK. Установка данных на выходе SDO - по спаду сигнала SCLK. Входные и выходные данные передаются старшим значащим битом вперед.

При использовании последовательного порта, на входах CSn, RDn, WRn должен присутствовать высокий уровень.

Рисунок 6.4. Временная диаграмма работы последовательного порта

Таблица 5. Команды последовательного интерфейса.

| Команда | Код      | Параметр | Новое        | Назначение                                            |

|---------|----------|----------|--------------|-------------------------------------------------------|

|         |          |          | значение     |                                                       |

|         |          |          | сдвигового   |                                                       |

|         |          |          | регистра     |                                                       |

| NOP     | 00000000 | data     | DEVID        | Нет операции. Значение data игнорируется.             |

|         |          |          | $(201_{16})$ |                                                       |

| SETA    | 00010000 | addr     | регистр      | Запись addr в адресный регистр.                       |

|         |          |          | адреса       |                                                       |

| WR      | 00100000 | data     | регистр      | Запись data в регистр по адресу в адресном регистре   |

|         |          |          | адреса       |                                                       |

| WRI     | 00110000 | data     | регистр      | Запись data в регистр по адресу в адресном регистре с |

|         |          |          | адреса       | последующей инкрементацией адресного регистра         |

| SETAFT  | 10110000 | addr     | прочитанные  | Запись addr в адресный регистр с выборкой значения    |

|         |          |          | данные       | регистра по адресу addr в сдвиговый регистр.          |

#### 6.4. Цифро-аналоговый преобразователь

Синтезатор оснащен двумя 10-разрядными ЦАП с дифференциальным токовым выходом. Каждый ЦАП может быть независимо переведен в режим низкого потребления установкой бита CTR.DACx on в «0».

Ток полной шкалы ЦАП задается резистором  $R_{REF}$ , включенным между выводом IREF и общим проводом, или источником тока, подключенным к IREF. Коэффициент масштабирования тока равен 128. Т.е. для получения номинального тока полной шкалы 10 мA, значение тока IREF должно составлять 78.13 мкA.

Напряжение на выводе IREF равно  $541\pm7$  мВ, таким образом, ток полной шкалы  $I_{FS}$  связан с резистором  $R_{REF}$  соотношением:  $I_{FS}$ =69.25B/ $R_{REF}$ .

Напряжение на выходах ЦАП OUTP, OUTM должно находиться в пределах  $\pm 0.6$ В относительно «земли».

### 7. ТИПОВЫЕ СХЕМЫ ВКЛЮЧЕНИЯ

#### 7.1. Двухканальный режим

Каждый канал ЦВС конфигурируется и используется независимо. Например, канал 1 может быть использован для формирования ЛЧМ сигнала, в то время как канал 2 формирует модулированный сигнал для передающего тракта цифровой системы связи. Частным случаем двухканального режима является квадратурный. В последнем случае настройки каналов различаются только начальной фазой синтезируемого сигнала.

# 7.2. Одноканальный режим

В одноканальном режиме, выходные сигналы с обоих каналов суммируются и подаются на оба ЦАПа. Возможные области применения данного режима:

- **ñ** Формирование двух каналов передачи данных;

- ñ Синтез QAM c GMSK;

- **ñ** Расширение динамического диапазона за счет параллельного включения двух ЦАПов.

# 7.3. Режим ЛЧМ с умножением частоты

В этом режиме ЦВС 1508ПЛ8Т используется совместно с целочисленным ФАПЧ для формирования ЛЧМ сигнала с девиацией в несколько гигагерц при сохранении высокой скорости и линейности изменения частоты.

Один канал используется в качестве источника опорной частоты для ФАПЧ, в то время как второй формирует управляющее напряжение для быстрой перестройки ГУН.

# 8. ЭЛЕКТРИЧЕСКИЕ ХАРАКТЕРИСТИКИ

Таблица 6. Электрические характеристики (AVDD=1.8B, VDD=1.8B, DVDD=3.3B, T=-60..+85°C)

| Параметр                                                                                                                                        | Обозначен<br>ие | Мин. | Тип.           | Макс. | Размерн<br>ость   |

|-------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|----------------|-------|-------------------|

| Тактовая частота:                                                                                                                               | f               |      |                |       | МГц               |

| максимальная                                                                                                                                    | c               | 1000 | 1100           | _     | ТИТ Ц             |

| минимальная                                                                                                                                     |                 | -    | -              | 0     |                   |

| Входной уровень                                                                                                                                 | P               | -10  |                | 5     | дБм               |

| Входной импеданс                                                                                                                                | Rcin            | 20   |                |       | кОм               |

| Входная емкость                                                                                                                                 | Ccin            |      |                | 12    | пФ                |

| ЦАП                                                                                                                                             |                 | •    |                | •     | •                 |

| Разрешение                                                                                                                                      | N               |      | 10             |       | бит               |

| Дифференциальная нелинейность                                                                                                                   | DNL             |      | 0.2            | 1     | LSB               |

| Интегральная нелинейность                                                                                                                       | INL             |      | 0.6            | 1.5   | LSB               |

| Максимальная частота преобразования                                                                                                             | Fs              | 1000 |                |       | МΓц               |

| Дифференциальный токовый выход                                                                                                                  | Iodacfs         | 5    |                | 20    | мА                |

| Диапазон выходных напряжений                                                                                                                    | Uodac           | -0.6 |                | 0.6   | В                 |

| Динамический диапазон, свободный от паразитных составляющих, в широкой полосе (0 – 500МГц), f =1000 МГц,  — Fo=26 МГц — Fo=126 МГц — Fo=284 МГц | SFDRW           | 52   | 67<br>63<br>56 |       | дБ<br>дБ          |

| Динамический диапазон, свободный от паразитных составляющих, в узкой полосе (Fo $\pm 1$ MГц), f =1000 МГц с                                     | SFDRN           | 80   |                |       | дБ                |

| Фазовые отклонения от $90^{\circ}$ по выходам квадратурных ЦАП в полосе $(0-400 {\rm M} {\rm \Gamma u})$ без компенсации                        | dφ              |      |                | 1     | Град              |

| Амплитудные отклонения по выходам квадратурных                                                                                                  |                 |      |                |       |                   |

| ЦАП в полосе (0 – 400МГц) без компенсации                                                                                                       | dA              |      |                | 0,5   | дБ                |

| Погрешность коэффициента усиления                                                                                                               | GE              | -10  |                | 10    | %ПШ               |

| Смещения нуля                                                                                                                                   | OE              |      | 1              | 25    | мкА               |

| Температурный коэффициент усиления                                                                                                              | TGE             |      |                |       | ppm/C             |

| Температурный коэффициент смещения нуля                                                                                                         | TOE             |      |                |       | ppm/C             |

| Фазовый шум при частоте выходного сигнала 10 МГц, на отстройке                                                                                  |                 |      | 1.45           |       | F /F              |

| - 1κΓι                                                                                                                                          |                 |      | -145           |       | дБн/Гц            |

| - 10κΓμ                                                                                                                                         |                 |      | -155           |       | дБн/Гц            |

| - 100κΓц                                                                                                                                        |                 |      | -165           |       | дБн/Гц            |

| - 1MΓ <sub>Ц</sub>                                                                                                                              |                 |      | -172           |       | дБн/Гц            |

| Фазовый шум при частоте выходного сигнала 20 МГц, на                                                                                            |                 |      |                |       |                   |